Программируемый элемент межсоединения: семейство Axcelerator оснащено запатентованным программируемым элементом межсоединения "металл-металл", который располагается между двумя верхними слоями металла. Это полностью исключает маршрутизацию и каналы межсоединений между логическими модулями (как это реализовано в традиционных ПЛИС), обеспечивая эффективную модульную морскую архитектуру. Отказы, как правило, имеют открытое замыкание, образуя при программировании постоянные пассивные низкоомные соединения, что обеспечивает самое быстрое распространение сигнала в отрасли. Кроме того, чрезвычайно малый размер этих межсоединений обеспечивает богатые ресурсы маршрутизации для семейства Axcelerator. Сама природа энергонезависимой технологии обратного предохранителя Actel обеспечивает превосходную защиту от пиратства и клонирования дизайна (технология FuseLock). Клонирование невозможно (даже если предохранитель не запрограммирован), поскольку битовый поток или файл программирования никогда не загружается и не хранится в устройстве. Обратный инжиниринг практически невозможен из-за сложности различения запрограммированных и незапрограммированных предохранителей, а также из-за метода программирования предохранительного устройства.

Логические модули: семейство Axcelerator компании Actel предлагает два типа логических модулей: регистровые (R-ячейки) и комбинационные (C-ячейки). Они позволяют реализовать более 4 000 комбинационных функций с 5 входами. R-ячейка содержит флип-флоп с асинхронным очищением, асинхронной предустановкой и низкими активными сигналами управления разрешением. Регистры R-ячейки имеют программируемую полярность тактового генератора, которая может быть выбрана для каждого регистра отдельно. Регистры R-блока имеют программируемую полярность тактового генератора, которая может быть выбрана регистрово, что обеспечивает большую гибкость (например, функциональность двойной скорости передачи данных может быть легко отображена в ПЛИС) при сохранении ценных тактовых ресурсов. Источник тактового генератора R-блока может быть выбран из жестко подключенных часов, маршрутизируемых часов или внутренней логики. Два C-блока, один R-блок, два буфера маршрутизации передачи (TX) и два буфера приема (RX) образуют кластер, а два кластера - суперкластер. Каждый SuperCluster также содержит отдельный буферный модуль (B), который поддерживает вставку буферов в сети с большим вылетом с помощью средств маршрутизации, что позволяет минимизировать системное время ожидания и повысить эффективность использования логики.

Встроенная память Как упоминалось ранее, каждый чип ядра имеет три (в меньших чипах) или четыре (в обычных чипах) встроенных блока SRAM на западной стороне чипа, каждый блок SRAM с переменным соотношением сторон имеет размер 4,608 бита. Доступные конфигурации памяти - 128x36, 256x18, 512x9, 1kx4, 2kx2 или 4kx1 бит. Каждый блок имеет отдельные порты чтения и записи, каждый из которых может быть настроен на разную ширину бита. Например, данные могут быть записаны в 8-битном формате, а считаны в 1-битном. Кроме того, каждый блок SRAM имеет встроенный блок управления FIFO. Этот блок управления позволяет сконфигурировать блок SRAM как синхронный FIFO без использования основного логического модуля, а ширина и глубина FIFO программируются. Помимо обычных флагов EMPTY и FULL, FIFO имеет программируемые флаги ALMOST-EMPTY (AEMPTY) и ALMOST-FULL (AFULL). Помимо логики флагов, встроенный блок управления FIFO содержит счетчики, необходимые для формирования указателей адресов чтения и записи, а также схемы управления для предотвращения нестабильности и некорректной работы. Встроенные блоки SRAM/FIFO можно каскадировать для создания более крупных конфигураций.

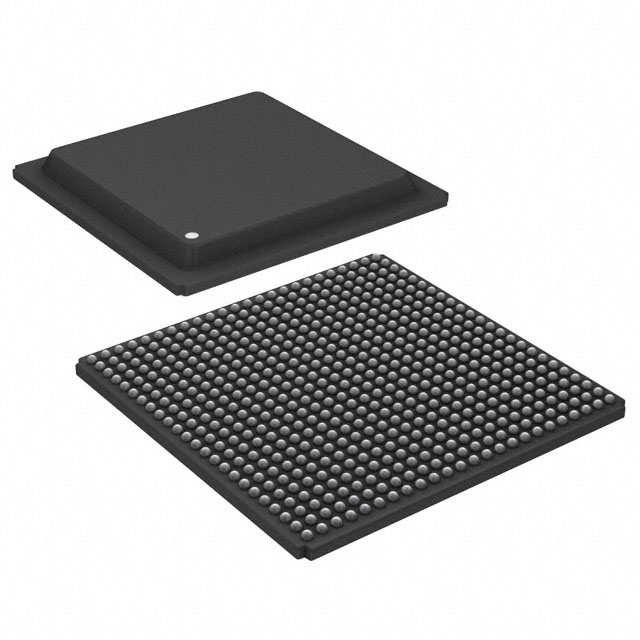

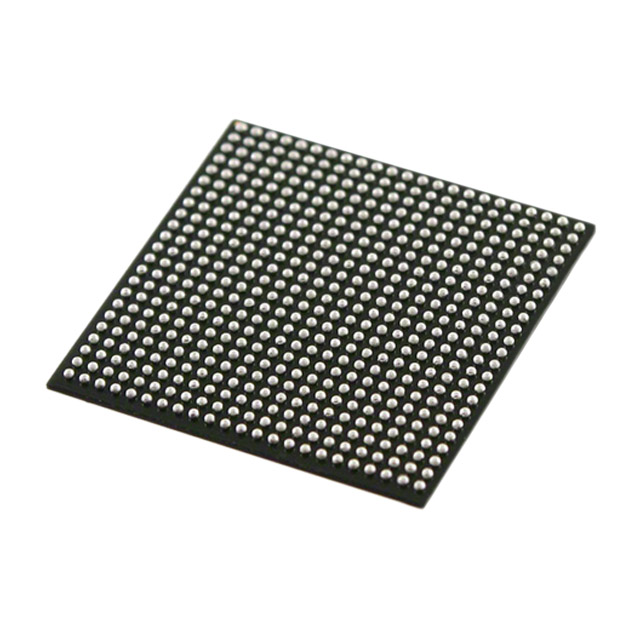

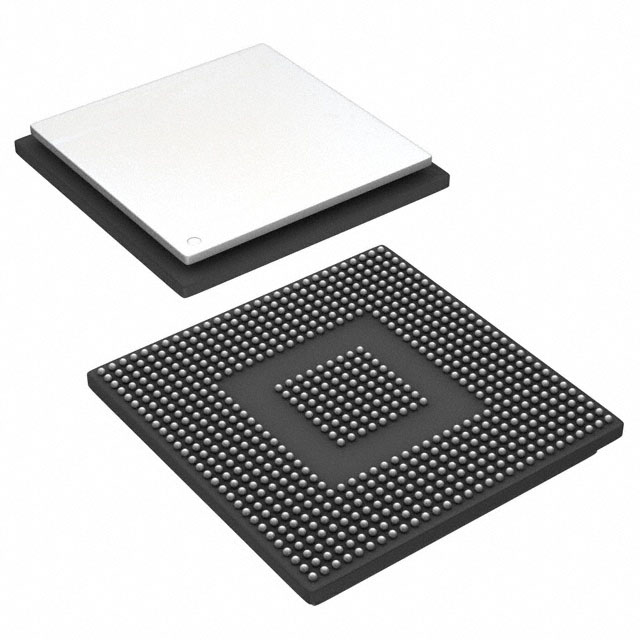

Интегральные схемы(ИС)

Интегральные схемы управления питанием (ПМИК) Преобразователи постоянного тока и переменного тока,автономные переключатели Зарядные устройства Управления батареей Текущее регулирование / управление Коммутационные контроллеры постоянного тока Драйверы дисплея Учет электроэнергии Драйверы Full и Half-Bridge Драйверы ворот Контроллеры горячей замены Драйвер лазерного диода Драйвер для светодиодов Контроллеры балластов ламп Драйверы и контроллеры двигателей, OR контроллеры/идеальные диоды Коррекции коэффициента мощности Переключатели распределения питания, драйверы нагрузки Управление питанием специализированное Контроллеры питания через Ethernet (PoE) Контроллеры и мониторы питания Преобразователи RMS в DC Регуляторы специального назначения Руководители Управление температурным режимом V/F и F/V преобразователи Опорные напряжения Регуляторы напряжения-Регуляторы коммутации постоянного тока Регуляторы напряжения-Линейные Регуляторы напряжения-Линейные + коммутационные Регуляторы напряжения- Контроллеры линейных регуляторов Интерфейс Аналоговые ключи-специального назначения Аналоговые ключи,мультиплексоры,демультиплексоры Кодеки Контроллеры Прямой цифровой синтез(ПЦС ) Драйверы, приемники, трансиверы Энкодеры, декодеры, преобразователи Активные фильтры Расширители ввода-вывода Модемы - ИС и модули Модули Интерфейсы датчиков и детекторов Емкостные сенсорные датчики Сериализаторы, десериализаторы Буферы сигналов, ретрансляторы, сплитеры Сигнальные терминаторы Специализированные Телеком УАПП Записи и воспроизведение звука Логические Буферы, драйверы, приемники, трансиверы Компараторы Счетчики, делители Памяти FIFO Триггеры Ворота, инверторы Ворота, инверторы-многофункциоальные,Конфигурируемые Защёлки Мультивибраторы Генераторы и поверочные устройства проверок на чет-нечет Сдвиговые регистры Переключатели сигнала, Мультиплексоры, Декодеры Специальные логики Переключатели,Трансляторы уровня Функции универсальной шины Сбор данных АЦП/ЦАП-специального назначения Аналоговый интерфейс АЦП цифровые потенциометры ЦАП Контроллеры сенсорных экранов Встраиваемые системы Специализированные микроконтроллеры Сложные программируемые логические устройства цифровые сигнальные процессоры ППВМ ППВМ с микроконтроллером Микроконтроллеры Микропроцессоры,микроконтроллеры,Модуль ППВМ Микропроцессоры Программируемые логические устройства Система на чипе Часы/Хронирование Специализированные часы/хронирование Тактовые буферы, драйверы Генераторы тактовых импульсов,петли фазовой автоподстройки частоты,Синтезаторы частоты Линии задержки ИС батареи Программируемые таймеры и осцилляторы Часы реального времени Линейные Усилители Аналоговые умножители и делители Компараторы Видеопроцесс Запоминающие устройства Аккумуляторы Программируемое ПЗУ для ППВМ Контроллеры Запоминающие устройства Специальные для аудио Специализированные микросхемы

Интегральные схемы(ИС)

Интегральные схемы управления питанием (ПМИК) Преобразователи постоянного тока и переменного тока,автономные переключатели Зарядные устройства Управления батареей Текущее регулирование / управление Коммутационные контроллеры постоянного тока Драйверы дисплея Учет электроэнергии Драйверы Full и Half-Bridge Драйверы ворот Контроллеры горячей замены Драйвер лазерного диода Драйвер для светодиодов Контроллеры балластов ламп Драйверы и контроллеры двигателей, OR контроллеры/идеальные диоды Коррекции коэффициента мощности Переключатели распределения питания, драйверы нагрузки Управление питанием специализированное Контроллеры питания через Ethernet (PoE) Контроллеры и мониторы питания Преобразователи RMS в DC Регуляторы специального назначения Руководители Управление температурным режимом V/F и F/V преобразователи Опорные напряжения Регуляторы напряжения-Регуляторы коммутации постоянного тока Регуляторы напряжения-Линейные Регуляторы напряжения-Линейные + коммутационные Регуляторы напряжения- Контроллеры линейных регуляторов Интерфейс Аналоговые ключи-специального назначения Аналоговые ключи,мультиплексоры,демультиплексоры Кодеки Контроллеры Прямой цифровой синтез(ПЦС ) Драйверы, приемники, трансиверы Энкодеры, декодеры, преобразователи Активные фильтры Расширители ввода-вывода Модемы - ИС и модули Модули Интерфейсы датчиков и детекторов Емкостные сенсорные датчики Сериализаторы, десериализаторы Буферы сигналов, ретрансляторы, сплитеры Сигнальные терминаторы Специализированные Телеком УАПП Записи и воспроизведение звука Логические Буферы, драйверы, приемники, трансиверы Компараторы Счетчики, делители Памяти FIFO Триггеры Ворота, инверторы Ворота, инверторы-многофункциоальные,Конфигурируемые Защёлки Мультивибраторы Генераторы и поверочные устройства проверок на чет-нечет Сдвиговые регистры Переключатели сигнала, Мультиплексоры, Декодеры Специальные логики Переключатели,Трансляторы уровня Функции универсальной шины Сбор данных АЦП/ЦАП-специального назначения Аналоговый интерфейс АЦП цифровые потенциометры ЦАП Контроллеры сенсорных экранов Встраиваемые системы Специализированные микроконтроллеры Сложные программируемые логические устройства цифровые сигнальные процессоры ППВМ ППВМ с микроконтроллером Микроконтроллеры Микропроцессоры,микроконтроллеры,Модуль ППВМ Микропроцессоры Программируемые логические устройства Система на чипе Часы/Хронирование Специализированные часы/хронирование Тактовые буферы, драйверы Генераторы тактовых импульсов,петли фазовой автоподстройки частоты,Синтезаторы частоты Линии задержки ИС батареи Программируемые таймеры и осцилляторы Часы реального времени Линейные Усилители Аналоговые умножители и делители Компараторы Видеопроцесс Запоминающие устройства Аккумуляторы Программируемое ПЗУ для ППВМ Контроллеры Запоминающие устройства Специальные для аудио Специализированные микросхемы Конденсаторы

Аксессуары Алюминиево-полимерные конденсаторы Алюминиевые электролитические конденсаторы Конденсаторные сети, массивы Керамические конденсаторы Электрические двухслойные конденсаторы (EDLC), суперконденсаторы Слюдяные и тефлоновые конденсаторы Конденсаторы из оксида ниобия Кремниевые конденсаторы Тантал - полимерные конденсаторы Танталовые конденсаторы Тонкопленочные конденсаторы Триммеры, переменные конденсаторы

Конденсаторы

Аксессуары Алюминиево-полимерные конденсаторы Алюминиевые электролитические конденсаторы Конденсаторные сети, массивы Керамические конденсаторы Электрические двухслойные конденсаторы (EDLC), суперконденсаторы Слюдяные и тефлоновые конденсаторы Конденсаторы из оксида ниобия Кремниевые конденсаторы Тантал - полимерные конденсаторы Танталовые конденсаторы Тонкопленочные конденсаторы Триммеры, переменные конденсаторы

Защита цепи

Автоматические выключатели Аксессуары для защиты цепей Электрические, специализированные предохранители Держатели предохранителей Предохранители Газоразрядные трубчатые разрядники (GDT) Прерыватели замыкания на землю (GFCI) Ограничители пускового тока (ICL) Защита освещения Сбрасываемые предохранители PTC ИКС для подавления импульсных перенапряжений Термовыключатели (термопредохранители) Подавители переходного напряжения (TVS)

Защита цепи

Автоматические выключатели Аксессуары для защиты цепей Электрические, специализированные предохранители Держатели предохранителей Предохранители Газоразрядные трубчатые разрядники (GDT) Прерыватели замыкания на землю (GFCI) Ограничители пускового тока (ICL) Защита освещения Сбрасываемые предохранители PTC ИКС для подавления импульсных перенапряжений Термовыключатели (термопредохранители) Подавители переходного напряжения (TVS)

Разъемы, межсоединения

Разъемы питания переменного тока Разъемы объединительной платы Разъемы типа "банан" и наконечники Бочкообразные разъемы Переходники между сериями Разъемы питания лезвийного типа Разъемы по краям карты Круглые разъемы Коаксиальные разъемы (RF) Контакты D-Sub, D-образные разъемы FFC, FPC (плоские гибкие) разъемы Волоконно-оптические разъемы Разъемы для тяжелых условий эксплуатации Разъемы Keystone Разъемы LGH Разъемы памяти Модульные разъемы Фотоэлектрические (солнечные панели) разъемы Подключаемые разъемы Прямоугольные разъемы Шунты, джамперы Гнезда для микросхем, транзисторов Разъемы для полупроводникового освещения Клеммные колодки Системы клеммных соединений Клеммные колодки и револьверные головки Клеммы Разъемы USB, DVI, HDMI

Разъемы, межсоединения

Разъемы питания переменного тока Разъемы объединительной платы Разъемы типа "банан" и наконечники Бочкообразные разъемы Переходники между сериями Разъемы питания лезвийного типа Разъемы по краям карты Круглые разъемы Коаксиальные разъемы (RF) Контакты D-Sub, D-образные разъемы FFC, FPC (плоские гибкие) разъемы Волоконно-оптические разъемы Разъемы для тяжелых условий эксплуатации Разъемы Keystone Разъемы LGH Разъемы памяти Модульные разъемы Фотоэлектрические (солнечные панели) разъемы Подключаемые разъемы Прямоугольные разъемы Шунты, джамперы Гнезда для микросхем, транзисторов Разъемы для полупроводникового освещения Клеммные колодки Системы клеммных соединений Клеммные колодки и револьверные головки Клеммы Разъемы USB, DVI, HDMI

Кристаллы, осцилляторы

Кристаллы, осцилляторы

Дискретный полупроводник

Транзисторы Биполярные (BJT) FETs, MOSFETs IGBTs JFETs Программируемый унипереход Специальное назначение Тиристоры DIACs SIDACs SCRs SCRs - модули TRIACs Диоды Мостовые выпрямители Выпрямители Радиочастотные диоды Переменная емкость (варикапы, варакторы) Зенер Регулирование тока - Диоды, транзисторы Модули драйверов питания

Дискретный полупроводник

Транзисторы Биполярные (BJT) FETs, MOSFETs IGBTs JFETs Программируемый унипереход Специальное назначение Тиристоры DIACs SIDACs SCRs SCRs - модули TRIACs Диоды Мостовые выпрямители Выпрямители Радиочастотные диоды Переменная емкость (варикапы, варакторы) Зенер Регулирование тока - Диоды, транзисторы Модули драйверов питания Индукторы, катушки, дроссели

Индукторы, катушки, дроссели

Изоляторы

Изоляторы

Карты памяти, модули

Карты памяти, модули

Реле

Аксессуары Автомобильные реле Контакторы (электромеханические) Контакторы (твердотельные) Высокочастотные (ВЧ) реле Стойки для релейных модулей ввода/вывода Релейные модули ввода/вывода Силовые реле, свыше 2 ампер Герконовые реле Релейные розетки Реле безопасности Сигнальные реле, до 2 ампер Твердотельные реле

Реле

Аксессуары Автомобильные реле Контакторы (электромеханические) Контакторы (твердотельные) Высокочастотные (ВЧ) реле Стойки для релейных модулей ввода/вывода Релейные модули ввода/вывода Силовые реле, свыше 2 ампер Герконовые реле Релейные розетки Реле безопасности Сигнальные реле, до 2 ампер Твердотельные реле

Резисторы

Резисторы

Датчики, преобразователи

Датчики цвета Датчики цвета - промышленные Датчики тока Энкодеры Энкодеры - промышленные Поплавковые датчики, датчики уровня Датчики поплавка, уровня - промышленные Датчики расхода Датчики расхода - промышленные Датчики силы Датчики силы - промышленные Датчики газа Датчики влажности, влажности Модули приемопередатчиков IrDA Преобразователи LVDT (линейный дифференциальный преобразователь) Магнитные датчики Магниты Датчики движения Многофункциональные Оптические датчики Датчики частиц, пыли Датчики положения Датчики давления, преобразователи Датчики давления, преобразователи - промышленные Датчики приближения Датчики приближения - промышленные Датчики приближения/занятости Готовые блоки Аксессуары для сенсорных кабелей Кабельные сборки датчиков Интерфейсные соединительные блоки для датчиков Аксессуары для датчиков, преобразователей Усилители для датчиков и преобразователей Датчики удара Солнечные элементы Специализированные датчики Датчики деформации Датчики температуры Сенсорные датчики Ультразвуковые приемники, передатчики Ультразвуковые приемники, передатчики - промышленные

Датчики, преобразователи

Датчики цвета Датчики цвета - промышленные Датчики тока Энкодеры Энкодеры - промышленные Поплавковые датчики, датчики уровня Датчики поплавка, уровня - промышленные Датчики расхода Датчики расхода - промышленные Датчики силы Датчики силы - промышленные Датчики газа Датчики влажности, влажности Модули приемопередатчиков IrDA Преобразователи LVDT (линейный дифференциальный преобразователь) Магнитные датчики Магниты Датчики движения Многофункциональные Оптические датчики Датчики частиц, пыли Датчики положения Датчики давления, преобразователи Датчики давления, преобразователи - промышленные Датчики приближения Датчики приближения - промышленные Датчики приближения/занятости Готовые блоки Аксессуары для сенсорных кабелей Кабельные сборки датчиков Интерфейсные соединительные блоки для датчиков Аксессуары для датчиков, преобразователей Усилители для датчиков и преобразователей Датчики удара Солнечные элементы Специализированные датчики Датчики деформации Датчики температуры Сенсорные датчики Ультразвуковые приемники, передатчики Ультразвуковые приемники, передатчики - промышленные

Трансформеры

Трансформеры

Русский

Русский